実際に製作してみて、設計通りの動きをするか確認します。

目次

試作

基板

ユニバーサル基板

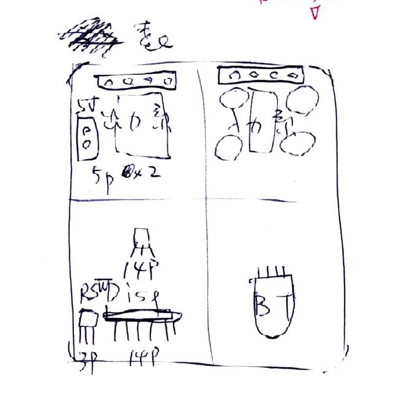

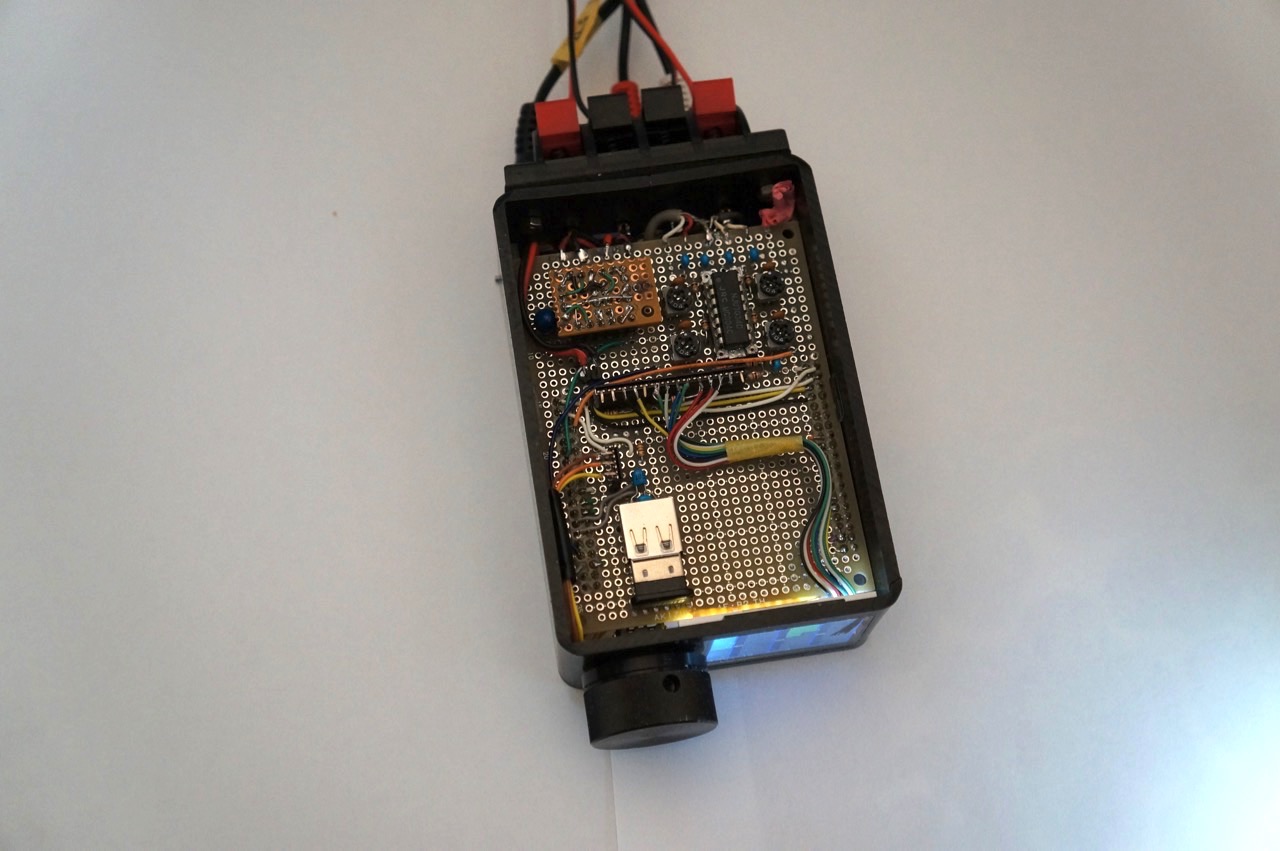

STM32-NUCLEOボードに、ユニバーサル基板を重ねる形で設計しています。ユニバーサル基板上の部品レイアウトは、大まかに以下の図のようにします。これは、デジタル回路のように最短配線ルートを重視したりするのではなく、アナログ系へのノイズ混入を心配して、ブロック分けにしてみました。

優先したいのがアナログ入力系の回路で、ノイズの影響を考えBT(Bluetoothドングル)と出来るだけ離します。本当は、スピーカドライバ(出力系)とも距離を置きたいところですが、それよりは画面の制御信号の方が、影響を及ぼしそうな気がしたので、結局赤字の絵のレイアウトにしました。実際は、BTの位置は左側にしています。

大まかなレイアウトが決まったら、部品の配置を考えます。

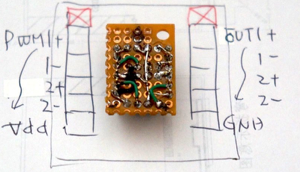

一品物なので、配線はPCB設計ツールを使わず、部品のピン位置を確認して配線ルート考えながら、実物の部品を差しながら丁度良い位置を決めて行きます。ここまで出来れば、大体頭の中に配線のイメージが固まるので、再確認しながら半田付けで配線して行きます。

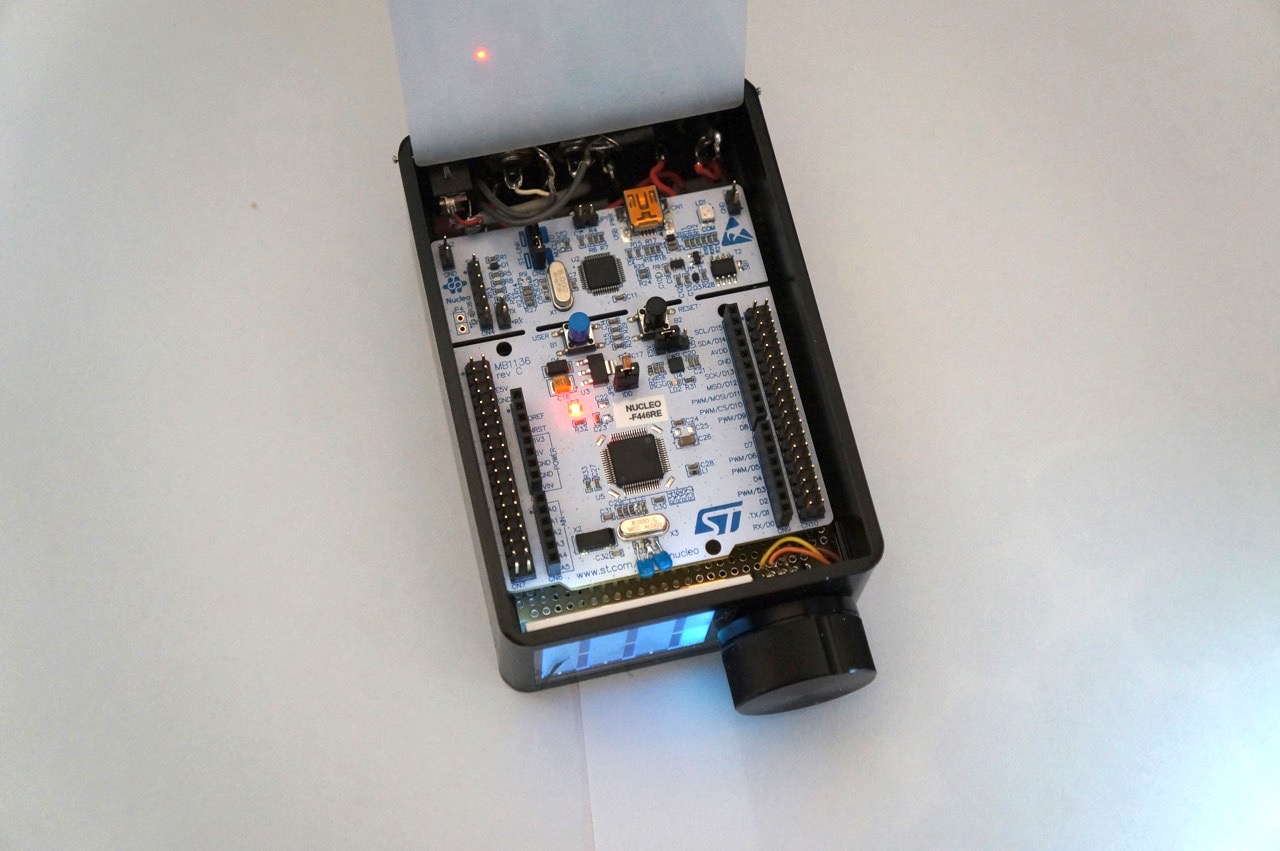

写真は、配線が終わった状態です。ヘッダピンのハウシング(左右に2つある黒いやつ)は裏面に取り付けるので、ユニバーサル基板はスルーホール型の物を使っています。

CPU基板(STM32-NUCLEO64)

NUCLEOボードも外部クリスタル8MHzを搭載する改修(改造)が必要です。そのほかに、何箇所か半田ブリッジを盛ったり、チップブリッジを取り除いたりする必要があります。詳しくは、回路図のコメントや、NUCLEOのユーザーズガイドを参照して下さい。

- ジャンパーJP5はE5V

- HSEを有効化(以下の改修)

- –X3に8MHzクリスタルを取り付け

- –C33,C34に20pを取り付け(試作ではむりやりリード品を使った)

- –ソルダブリッジSB54,SB55を取り除く

- –R35,R37をショート(半田を盛る)

- –ソルダブリッジSB16,SB50を取り除く

(NUCLEOボードは改修前の状態)

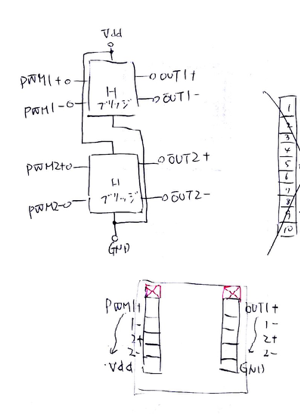

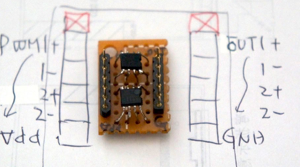

スピーカドライバサブ基板

スピーカドライバ部分は、前回色々と試行錯誤した経緯があり、容易に改修可能にしておきたいと思ったので、ICソケットを使ったサブ基板にします。これだと、基板を傷めずに、色々なデバイスを試してみるといった事が可能になります。

6P×2列のワイドDIPの形に設定しました。素のMOS-FETへの置き換えも可能なような端子にしています。 今回採用したHブリッジコントローラBD6211はSOP8パッケージ品で、細かい半田付け作業が必要ですが、私は細い線でSOP8の足を延長して浮かせた形でユニバーサル基板の穴に合わせるという工法を用いました。放熱的に何らかの対策が必要だと思われますが、まだ未対応です。実測で30℃位になっていますし、熱遮断機能があるので大丈夫と判断しました。裏側は、汚いですが間違いがなければ問題ありません。

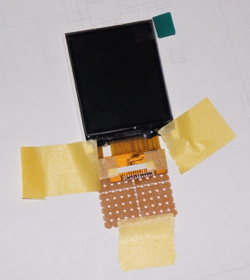

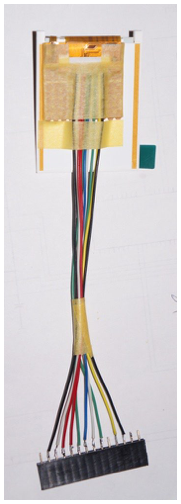

LCDモジュール

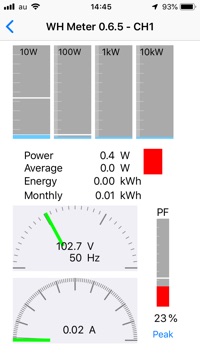

LCDモジュールは、0.8mmピッチのFPCなので工作しにく部分です。

変換ボードも売っているので、これを利用するのが楽だと思いますが、今回はケーススペースの制約から、使用できなかったので、電線を直接半田付けする工法としました。電線は柔軟性がある複線タイプにしたかったのですが、0.8mm以下の細いものは単線しか手持ちがなかったので、FPCに力が加わらないようにユニバーサル基板で補強するようにしました。これでも「ねじり」が入ると、FPCに応力がかかるので、取り扱いも細心の注意が必要です。やはり、複線タイプの電線にするべきでした。

結線確認と火入れ

結線確認は、 テスタで導通チェックで行います。配線中にも随時行いますが、最後に以下のチェックを行います。

•電源ラインが各部品につながっているか、

•同様にGNDラインが行き渡っているか

•電源とGNDがショートしていないか

•主要なラインの結線

問題なしだったので、火入れ(電源投入)します。

•外せる部品は全て外す

•半固定抵抗は全て中間位置

•STM32-NUCLEOボードを載せない状態で電源接続

•電流が異常に流れたら即OFF、各部品の発熱も指で触れて確認

•各部品の電源電圧をチェック

•全部品、STM32-NUCLEOボードを載せて電源を再度投入

•電流が異常に流れたら即OFF

焦げ臭かったり、発熱する部品もないようだったので、特に問題なしのもよう。

動作確認

アナログ入力部

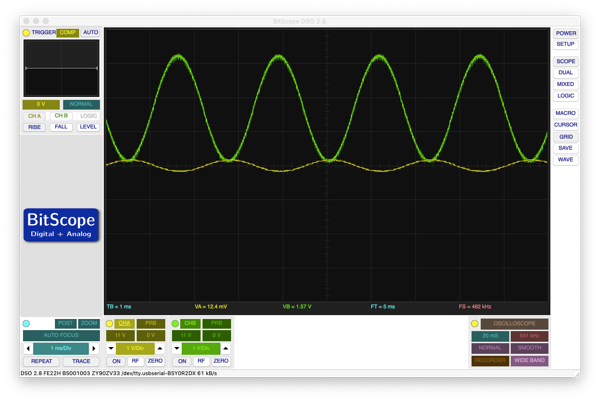

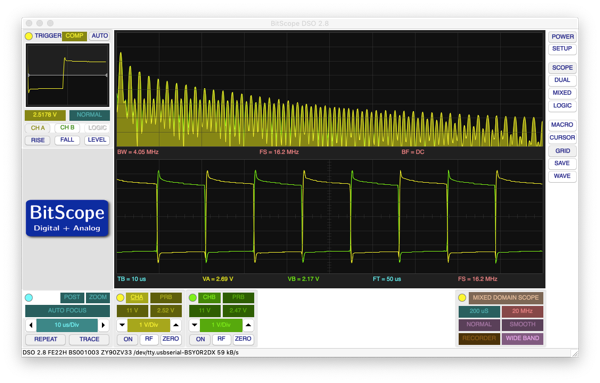

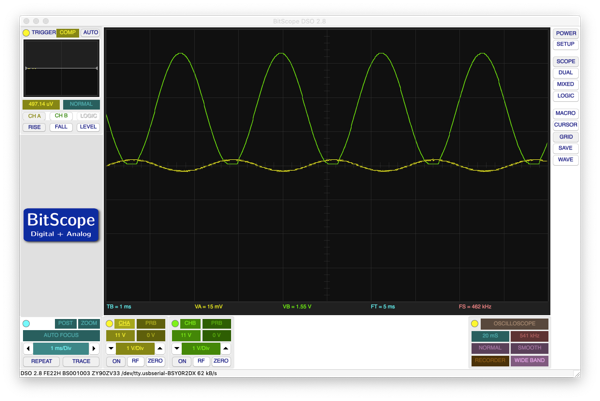

テスト用の音源をつなげて、オペアンプの出力(マイクロコントローラのアナログ入力)に信号が現れるか確認。

テスト用の音源は440Hzの正弦波で、黄が入力、緑がオペアンプの出力です。反転増幅は正常に機能しているようです。振幅も0〜3.3Vで問題ありません。波形に細かいノイズが乗っているように見受けられます。耳で聞くと、無音時にホワイトノイズが大きく感じます。また、Bluetoothが通信を行うとノイズが入り込む現象を確認しました。

なお、440HzはPCでWAVファイルを再生させ、ヘッドフォン出力でつなげたものです。

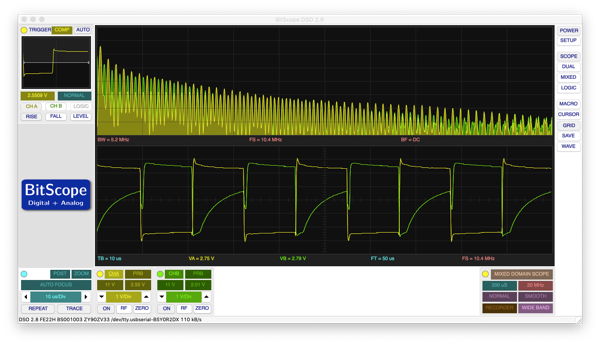

スピーカ出力部

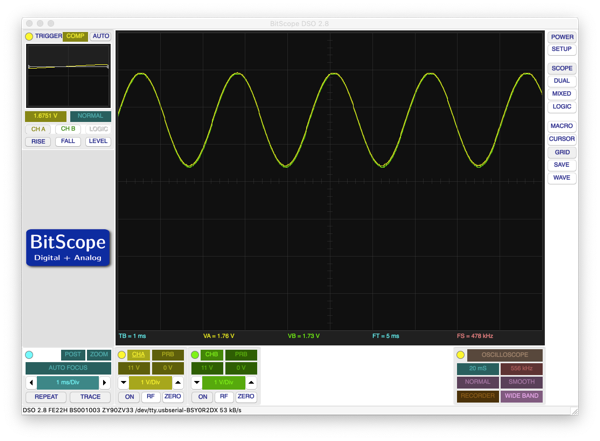

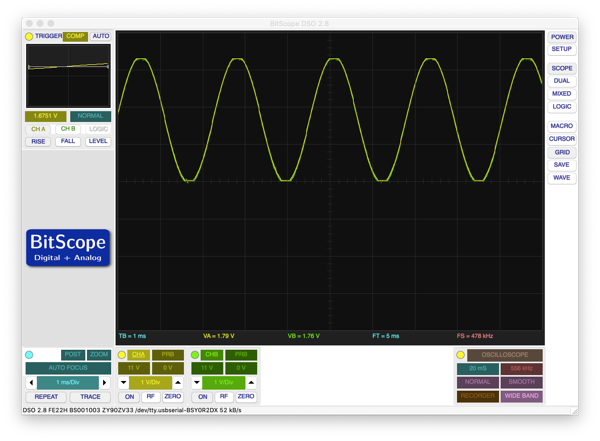

これは、インピーダンス8Ωのスピーカを接続したときの出力波形です。入力信号は無音時です。

黄色が+側、緑色がー側です。50%Dutyで+/ー相互に入れ替わる様子が確認できます。左側の波形はおかしいです。実際耳で聞いても左側の音量が小さく感じます。右側のスピーカは、きれいな波形です特に問題はないようです。

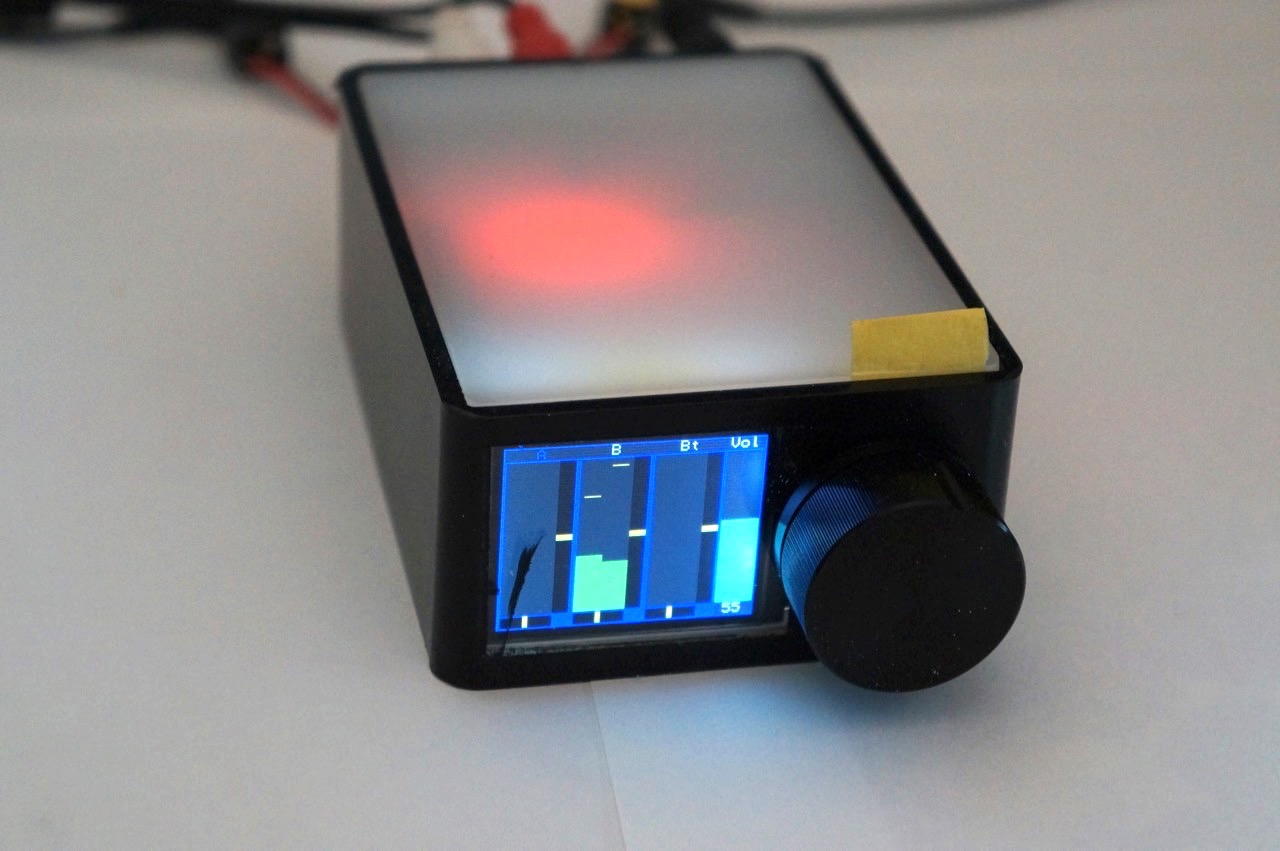

表示/操作部

ソフトウェア開発しながらの確認となりましたが、特に問題はありませんでした。

消費電力

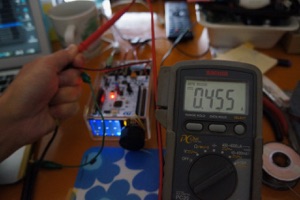

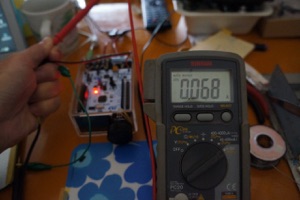

DCプラグ部分で電流を計測します。(8Ωスピーカを接続)

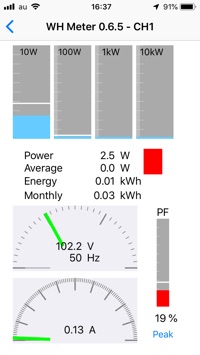

左は稼働中、右はスタンバイ中。

AC上の消費電力を計算すると、

動作中: 0.455A * 5V / 0.8 = 2.84W(DCアダプタの効率を80%とした場合)

スタンバイ中:0.068A * 5V / 0.8 = 0.43W

前作では、ボリューム位置に応じて消費電力が変わりましたが、ボリュームを変えても大きな変化はありません。ある意味、設計通りなのですが、改めて確認すると「何とかならないものか」と考えてしまいます。まあ、3Wぐらいなので気にしなくても良いレベルなのですが。

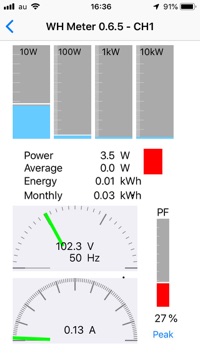

裏付けとして、AC上での消費電力測定を「WHM0.6.5」で計測してみました。

左から最大ボリューム時、最小ボリューム時、アイドル時の値です。

3.5〜2.5Wなので、おおむね合致します。スタンバイ時の値も合っています。

外装

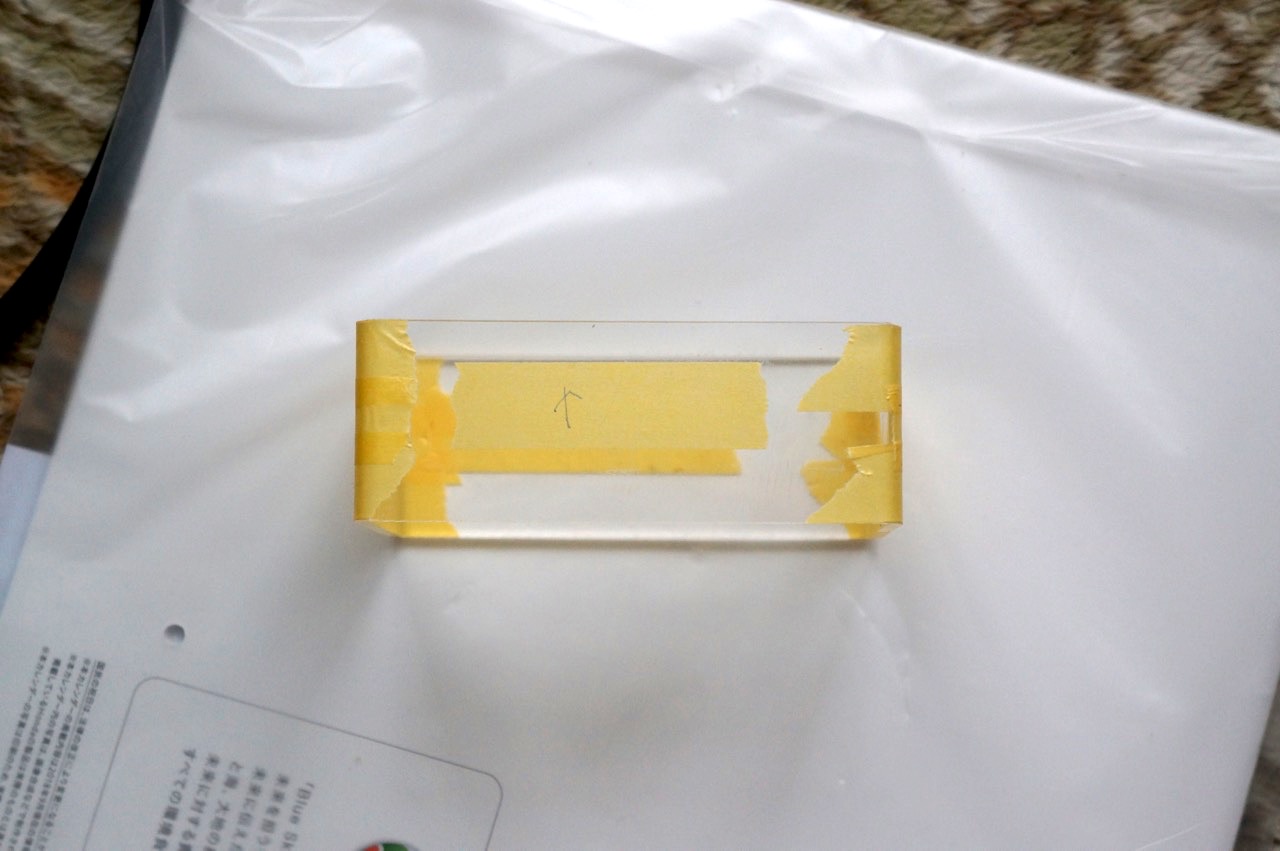

ケース

アクリル板の工作に慣れていない方は、先に別文書をご参照ください。

設計図の通りに製作します。3mmの透明アクリル板をヒーターで曲げて、底のない弁当箱状態にします。透明以外の材料を使う場合、表示窓部分をくり抜かなければなりません。

スケルトン状態なので、作業的には色々とやりやすいです。サイズ的にぎりぎりの設計なので、部品間の干渉には特に気を使ったので、問題が出なかったのには安堵しました。上面には、乳白色の天板をヒンジで開くようにしています。基板の固定は、ケース幅=基板幅にしたので、ねじ止めではなく、アクリル板の小片で基板を挟み込む方法にしました。ケースの側板を広げれば、基板が外れる仕組みです。(写真を拡大して確認してみて下さい)

塗装

表示窓以外を外側から塗装します。内側を塗装する方法では、傷には強くなりますが、色々と不都合なことが多いのでやめておきます。

組み立て

パネル部品を取り付け、ユニバーサル基板を取り付けます。最後にCPU基板を載せたら完成です。

問題点と対策

下記の問題点が見つかりました。

- アナログ入力でホワイトノイズが大きい

- アナログ入力にBluetoothの通信が入り込む

- 左側のスピーカ出力波形が異常

アナログ入力のホワイトノイズ

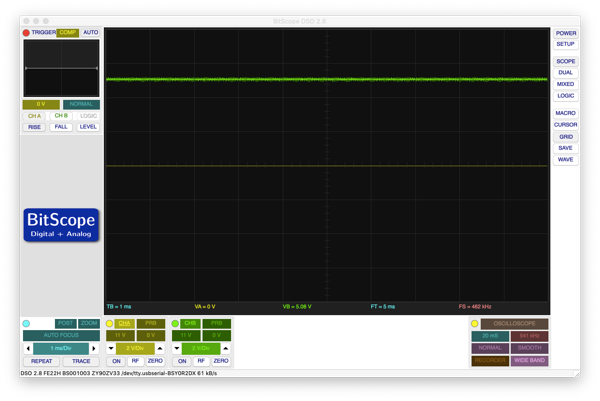

波形を見ても、あまりきれいなものではないので、どこかからかノイズが混入するパターンだと考えられます。一番最初に疑われるのは電源ライン、次にオペアンプ内、近接デバイスからの電磁結合などがあります。まずは、5V電源ラインのチェック。

やはり、あまりきれいな電源ではない事が判明しました。本当は、この問題は設計時に予期していたことで、どれだけノイズが乗ってくるか分からなかったので、実際動かして確認/対処する事にしていました。

対策としては

•電源ラインにノイズフィルタ(ローパスフィルタ)を追加

•電源を3.3Vに変更する

前者は、部品追加で比較的簡単に対応可能。後者は、オペアンプの品種を変えて、回路も若干改造すれば対応可能。対応が簡単な前者を実施する事にしました。

アナログ系に与える5V電源ラインの間に100HzローパスLCフィルタを追加しました。定数は100μH+10μFの組み合わせです。スッキリした波形に変わり、大きな効果がありました。耳で聞いても激減しました。

アナログ入力のBluetoothノイズ

Bluetoothドングルには、青色のLEDが付いており、電波を出すと点滅します。それと同期して「プツプツ」「ピーポロポロ」といった信号が紛れ込むので、ノイズ源は特定できますが、伝達ルートがわかりません可能性を考えてみました。

•電源ライン経由のノイズ(ドングルも5V電源を使っている)

•Bluetoothの電波がどこかの部品に入り込んで、そこから伝わる

•前作では、このような問題は全くないので、その違いの中にある

まずは、 ノイズの入り込んでいる部分を全て調べ、伝達ルートを絞り込みます。

•オシロスコープの波形で確認 ‥‥大きなノイズではないので判別は難しい

•イヤホンを使って「音」を聞いてみる ‥‥やろうと思えば出来る

イヤホン式だとスピーカから出る音と聞き比べながら確認できるので、確認作業はやりやすいと思います。以前にもやった事があるかもしれませんが、試しに実施してみました。もう数秒で判明。5V電源ラインにその音が乗っていました。ローパスフィルターでも取り除けなかったノイズです。3.3V電源ラインは静かなものです。

対策は、すでにノイズフィルタを加えていますので、それを見直してノイズを取り除くというやり口よりは、ノイズのない3.3V電源に変更する方が確実と考えました。コスト的には、大きな差異はありませんし、回路的には単純になるので歓迎できるものです。とは言え、最初の設計時の考慮が足りなかったと反省しなければなりませんが、ノイズ

対応された回路図バージョンは「0.2a」です。

当然のことながら、改修後はノイズが全く入り込まなくなりました。

オペアンプの品種がフルスイング対応のものに変更となりますので、一応波形を確認です。

かなりはっきりした波形になりました。下は、わざと飽和する信号を加え、最大最小レベルを確認してみたところです。当然ながら0〜3.3Vに収まっています。

左側のスピーカ出力波形が異常

波形から想定すると、Hブリッジを構成するFETの内、1素子だけ機能していないような感じを受けます。前作で試験的に使った個体なので、その時に壊してしまった可能性が考えられます。

試行錯誤的にはなりますが、左側のドライバICのBD6211を新しい物に交換したら、直りました。設計上の問題ではなく、製造上の問題でした。サブ基板にしていたので作業も簡単、目論見通りです。その後、改良作業を行ううちに、また左側が壊れてしまいました。左側だけが壊れる理由があるのでしょうか。よく考えると、測定は左側だけで行っていました。今回使用しているオシロスコープは、PC接続の非絶縁タイプなので、グラウンドには注意を払わなければなりません。もし、スピーカ端子間の相対電圧を測定する時に、測定端子以外にPCと被測定対象と電気的に接続してしまったら大電流が発生してしまいます。多分、このルートで素子破壊になってしまった可能性が高いです。今後、十分に注意するべきです。

Copyright©2019 Toyohiko TOGASHI

コメントを残す